Samsung may have accidentally revealed that it is developing a RISC-V CPU/accelerator.

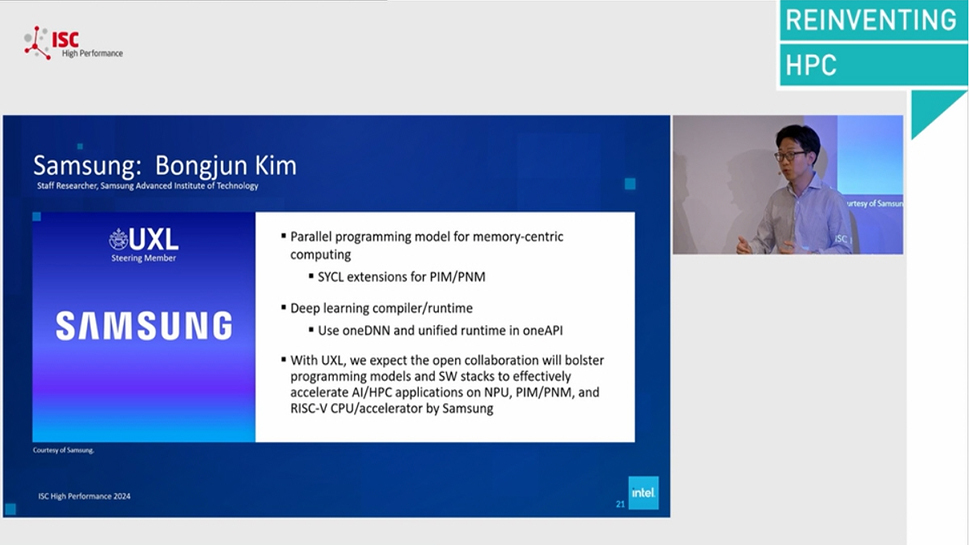

The slip happened during a session titled “Unlocking the Next 35 Years of Software for HPC and AI” at the recent ISC conference, where a slide talking about the UXL Foundation (Unified Acceleration Foundation), mentioned a “RISC-V CPU/AI accelerator from Samsung.”

This has sparked speculations about the South Korean tech giant’s plans to integrate RISC-V architecture in its upcoming technologies, specifically in its Mach-1 AI accelerator chip which is expected to arrive early in 2025.

Not actually the first mention

Samsung is a steering member of the UXL Foundation, as is Arm, Qualcomm, Intel and Google Cloud. UXL develops software aimed at enhancing AI accelerators that do not use Nvidia’s GPUs – an alternative to Nvidia’s CUDA in other words.

The Mach-1 is reportedly a ‘lightweight’ AI chip, utilizing low-power (LP) memory instead of the costly HBM typically used in AI semiconductors. Naver, the South Korean equivalent of Google, has signed a 1 trillion won ($750 million) agreement with Samsung for Mach-1 chips.

RISC-V, an open-standard instruction set architecture, is rapidly gaining traction as it allows any developer to build their own processors without costly licensing fees. Details about Samsung’s RISC-V CPU’s capabilities remain sparse, but HPCwire speculates that the CPU “could be a low-performance RISC-V processor in Samsung’s memory-based chip to run specific tasks defined by software kit functions.” That would fit with what we know about the Mach-1 and make sense as RISC-V doesn’t offer the same performance as Intel’s x86 chips.

A number of hardware manufacturers, including Apple and Nvidia, already use RISC-V microcontrollers in their products, and countries like Europe, China, and Russia are developing their own sovereign chips based on RISC-V CPUs as part of a broad industry trend towards diversification and independence from proprietary technologies.

A little digging reveals that Samsung has referenced the existence of a RISC-V CPU/accelerator before. In a Linux Foundation webinar a month ago, again about the UXL Foundation, it appeared in a slide there too.

+ There are no comments

Add yours